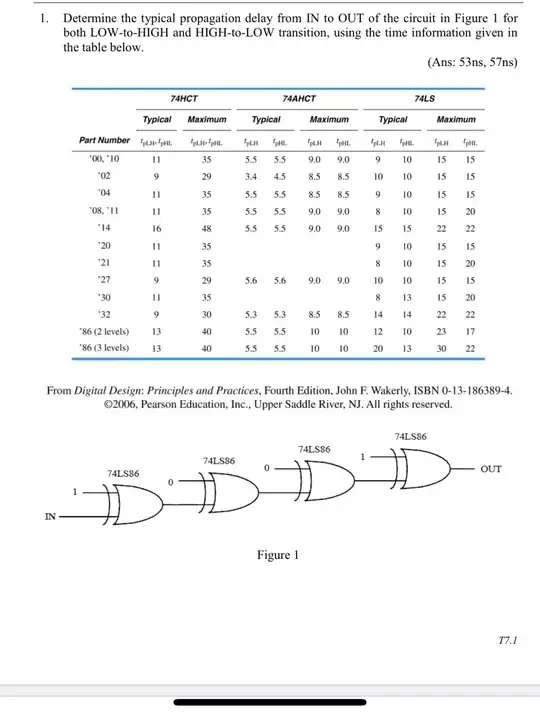

Since it is typical propagation delay, and it is 74LS86, I will have to use the table on the typical Column with the 86 “2 levels” row right? And how do I get on from here? Correct me if I’m wrong please. I can’t seem to figure out how to calculate.. Thank you

1 Answers

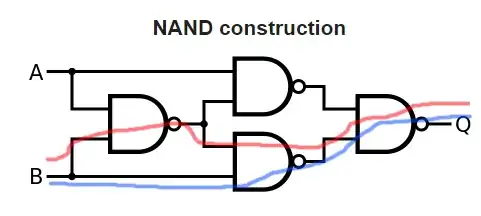

The trick to this question is understanding how an XOR is constructed. V.V.T had the correct answer.

The blue path is the longest when "A" is low, the leftmost NAND output is high regardless of the "B" input.

The red path is the longest when "A" is high.

I can't find any documentation that indicates that this is how a 74LS86 is constructed, but a NAND gate is a basic building block for TTL so it is likely. I am guessing that this gate implementation is buried in the textbook somewhere, or was included in datasheets back when this textbook was written (old textbook).

image from: https://en.wikipedia.org/wiki/XOR_gate (annotated by me)

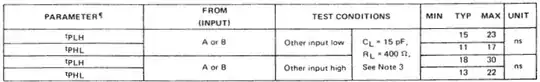

Edit: Here is a spec from a TI 74LS86 datasheet. The numbers don't match what the OP posted, but the fact that the prop delay is dependent on the state of the other input is clear. I admit that the NAND implementation is a guess, but in any case, there are 3-levels of gates, transistors or whatever; and one of them is bypassed when the other input is low.

- 15,935

- 1

- 20

- 47

-

This seems unlikely to me. First, the table actually provides data for the LS86 so there is no need to make assumptions about how it is constructed. Second, the propagation delay for gates buried within an SSI device will be much different (less) than the propagation for a discrete gate. So, the table does not provide data that could be used to answer the question if your approach is needed. – Elliot Alderson Oct 16 '20 at 21:19

-

@ElliotAlderson - This interpretation gives the correct answer according to td127. Do you have a better explanation for the 2 and 3 level specs? – Mattman944 Oct 16 '20 at 21:32

-

Well, getting the provided answer is not the same as getting the correct answer. I will accept that your method could yield the answer that the OP was looking for. – Elliot Alderson Oct 16 '20 at 22:09

'86(other input high)... . – V.V.T Oct 14 '20 at 07:57